# Novel Test Point Insertion Applications in LBIST

by

Yang Sun

A dissertation submitted to the Graduate Faculty of Auburn University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

> Auburn, Alabama Dec 11, 2021

Keyword: Artificial Neural Network, Test Point Insertion, Logic Built-in Self-Test, Test Power

Copyright 2021 by Yang Sun

Approved by

Spencer K. Millican, Chair, Assistant Professor of Electrical and Computer Engineering Vishwani D. Agrawal, Professor Emeritus of Electrical and Computer Engineering Adit D. Singh, Godbold chair, Professor of Electrical and Computer Engineering Ujjwal Guin, Assistant Professor of Electrical and Computer Engineering

#### Abstract

Pseudo-random stimulus is an established industry practice due to its simplicity and significant fault coverage. However, when applied to modern circuits, pseudo-random stimulus can fail to excite and observe *random pattern resistant* (RPR) faults. These faults become more common as logic circuitry becomes more complex, which naturally occurs with technology scaling. Many techniques attempt to detect RPR faults using *logic built-in self-test* (LBIST), including (1) modifying the pattern generator to create less "random" stimulus or (2) modifying circuits to make RPR faults more easily tested with random stimulus. This latter method, known as *test point* (TP) *insertion* (TPI), is frequently used in industry due to its ability to be implemented on post-synthesis circuit netlists with minimal effort from circuit designers. Optimal TPI is known to be an NP-hard problem, thus current TPI methods use heuristics to overcome computational barriers. *Artificial neural networks* (ANNs) are computing paradigms that present opportunities to increase solution quality and overcome computational barriers imposed by heuristic algorithms.

This dissertation studies ANN TPI algorithms. The methods include collecting training data, training ANNs, and analyzing ANNS to evaluate TPs. Experiments compare ANN-based TPI methods against equivalent heuristic algorithms in terms of circuit testability and computation time. Experimental results show ANN-based TPI can achieve high fault coverage with less execution time.

Another concern for *design-for-test* (DFT) engineers is high test power since high-power tests can cause false failures and circuits become less reliable when large and instantaneous power dissipation causes overheating. Thus, techniques must reduce test power while keeping fault coverage acceptable. Control TPs can reduce switching activity and keep lines stable, thus decrease power consumption during test. However, control TPs may also cause fault coverage to decrease, thus some strategies must be used to balance power and fault coverage. This dissertation proposes power-targeting TPI. The method uses multi-phase strategies in power-targeting TPI to minimize the negative impacts on fault coverage. Experiments compare different numbers of TPI phases and finds the best number of TPI phases, and experimental results show power-targeting TPI can reduce test power while keeping fault coverage high.

#### Acknowledgments

Firstly, I am very grateful to my advisor Prof. Spencer K. Millican for his guidance. He inspired me a lot whenever I had problems with my research work. I also appreciate my other committee members: Prof. Vishwani D. Agrawal, Prof. Adit D. Singh, and Prof. Ujjwal Guin. They gave me lots of suggestions and helpful comments, so that I can modify and improve my dissertation research. Besides these professors, I would like to thank my team members, who helped me a lot in my research field. I couldn't have made a success in my research and other projects without their help. Last but not the least, I want to thank my family members and friends, who give support with their love during my whole study in Auburn.

# Table of Contents

| Abstract.         | ii                                           |

|-------------------|----------------------------------------------|

| Acknowle          | dgmentsiv                                    |

| Table of <b>(</b> | ontentsv                                     |

| List of Fig       | uresviii                                     |

| List of Ta        | ples xi                                      |

| List of Al        | breviationsxii                               |

| Chapter 1         | Introduction1                                |

| Chapter 2         | Background 5                                 |

| 2.                | TP Architectures                             |

| 2.5               | TP Selection Architectures7                  |

| 2.                | TPI Algorithms                               |

| 2.4               | Modern Targets for TPI 14                    |

| Chapter 3         | Introduction to ANNs17                       |

| 3.                | ANNs history                                 |

| 3.:               | ANNs structures                              |

| 3.                | Training ANNs 19                             |

| 3.4               | ANN applications                             |

| Chapter 4         | ANNs TPI Targeting Stuck-at Fault Coverage21 |

| 4.                | Introduction to the Stuck-at Fault Model21   |

| 4.                | Proposed Method                              |

| 4.                | ANN Input                                    |

| 4.                | Output Label                                 |

| 4.5         | Training Data Generation                          | 25 |

|-------------|---------------------------------------------------|----|

| 4.6         | Training                                          | 27 |

| 4.7         | ANN TPI Flow                                      | 27 |

| 4.8         | Experiment Results                                | 28 |

| 4.9         | Conclusion                                        | 37 |

| Chapter 5 A | NNs TPI Targeting Transition Delay Fault Coverage | 38 |

| 5.1         | Introduction to the Transition Delay Fault Model  | 38 |

| 5.2         | Proposed Method                                   | 39 |

| 5.3         | Input Features                                    | 40 |

| 5.4         | Output Label                                      | 40 |

| 5.5         | Training Data Generation                          | 41 |

| 5.6         | Training                                          | 42 |

| 5.7         | Experiment Results                                | 42 |

| 5.8         | Conclusion                                        | 47 |

| Chapter 6 D | evelopments in ANN TPI                            | 48 |

| 6.1         | ANN Input Feature Development                     | 48 |

| 6.2         | ANN Output Label Development                      | 48 |

| 6.3         | Experiment Results                                | 49 |

| Chapter 7 T | est Power Reduction through Test Point Insertion  | 59 |

| 7.1         | Introduction                                      | 59 |

| 7.2         | Background                                        | 61 |

| 7.3         | TPI for Power Reduction                           | 64 |

| 7.4         | Experiment Results                                | 66 |

|         | 7.5   | Conclusion and Future Directions | 75 |

|---------|-------|----------------------------------|----|

| Chapter | 8 Co  | nclusion and Future Work         | 76 |

| Bibliog | raphy |                                  | 77 |

# List of Figures

| Figure 2.1: Logic-level implementations of control, inversion, and observe TPs                       |

|------------------------------------------------------------------------------------------------------|

| Figure 3.1: An example of a) a single neuron, and b) the ANN prototypical structure                  |

| Figure 4.1: A sub-circuit size is represented by <i>L</i> levels. "X" marks the TP location          |

| Figure 4.2: A conversion of a sub-circuit to the format of no more than two fan-in/fan-out per gate. |

|                                                                                                      |

| Figure 4.3: The ANN input features are CC, CO, Gate type                                             |

| Figure 4.4: ANN TPI Flow                                                                             |

| Figure 4.5: A plot of training time's impact on ANN accuracy                                         |

| Figure 4.6: A plot on the number of neuron's on ANN accuracy                                         |

| Figure 4.7: A plot of training data size on ANN accuracy                                             |

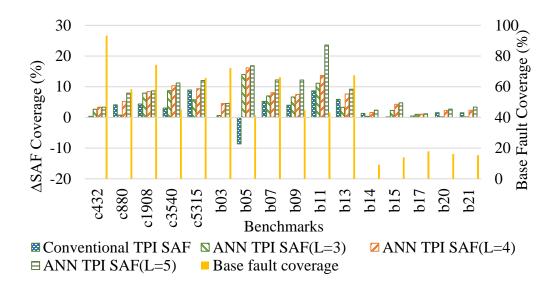

| Figure 4.8: ANN and conventional TPI targeting SAF in SAF coverage comparison                        |

| Figure 4.9: ANN and conventional TPI targeting SAF in time comparison                                |

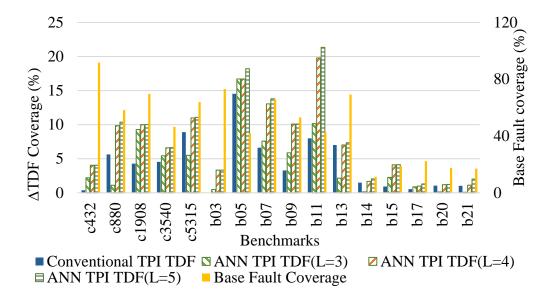

| Figure 5.1: ANN and conventional TPI targeting TDF in TDF coverage comparison                        |

| Figure 5.2: ANN and conventional TPI targeting TDF in SAF coverage comparison                        |

| Figure 5.3: ANN and Conventional TPI targeting TDF in time comparison                                |

| Figure 6.1: Increasing ANN training data typically increases ANN accuracy, but also increases        |

| training time                                                                                        |

| Figure 6.2: Increasing ANN complexity can decrease ANN error, but training time also increases.      |

|                                                                                                      |

| Figure 6.3: Different sub-circuit size ANN TPI and conventional TPI in SAF coverage comparison.      |

|                                                                                                      |

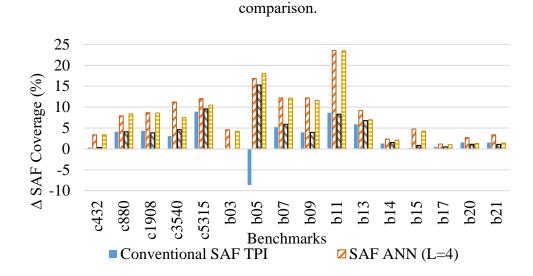

| Figure 6.4: SAF targeting conventional and ANN TPI may not increase SAF coverage compared         |  |

|---------------------------------------------------------------------------------------------------|--|

| to their TDF targeting counterparts 55                                                            |  |

| Figure 6.5: Different sub-circuit size ANN TPI and conventional TPI in TDF coverage comparison.   |  |

|                                                                                                   |  |

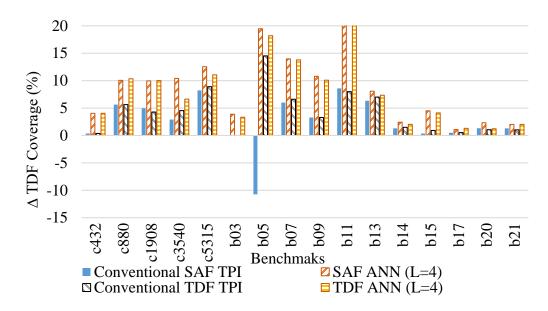

| Figure 6.6: TDF targeting conventional and ANN TPI may not increase TDF coverage compared         |  |

| to their SAF targeting counterparts                                                               |  |

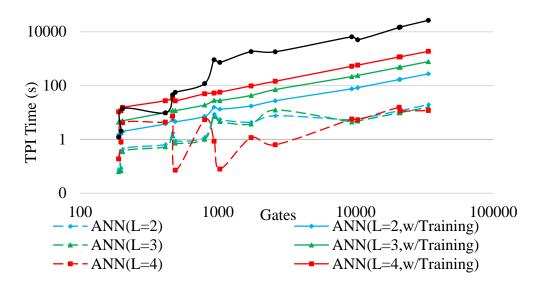

| Figure 6.7: Conventional TPI and different sub-circuit ANN TPI in time comparison                 |  |

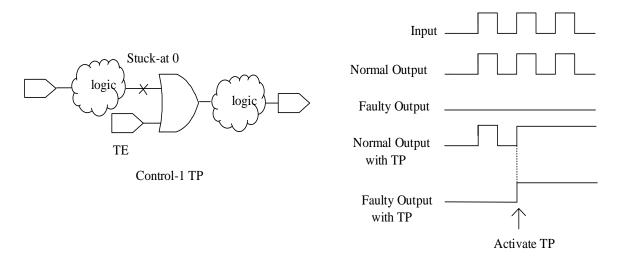

| Figure 7.1: Control TPs can reduce switching activity, but also block faults                      |  |

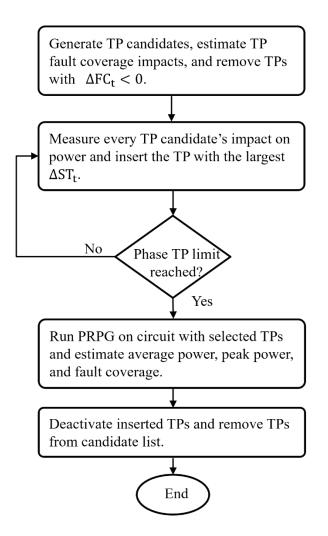

| Figure 7.2: Flow chart of multi-phase TPI                                                         |  |

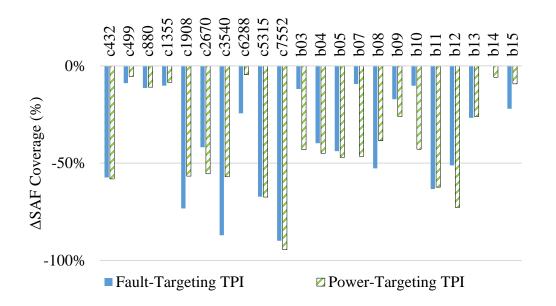

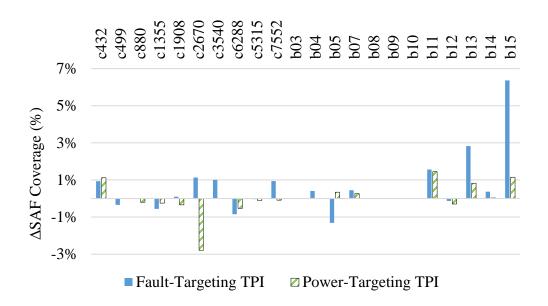

| Figure 7.3: Power-targeting TPI and conventional fault-targeting TPI in SAF coverage comparison.  |  |

|                                                                                                   |  |

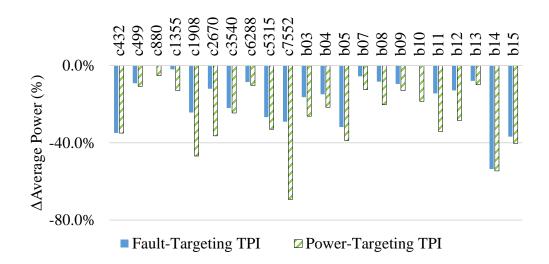

| Figure 7.4: Power-targeting TPI and conventional fault-targeting TPI in average power             |  |

| comparison                                                                                        |  |

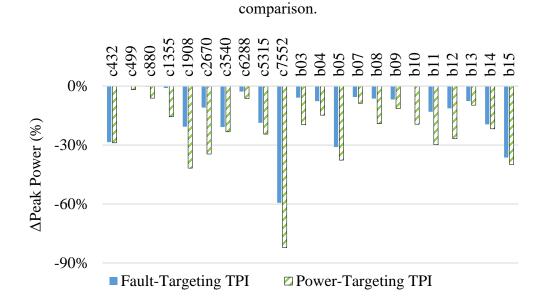

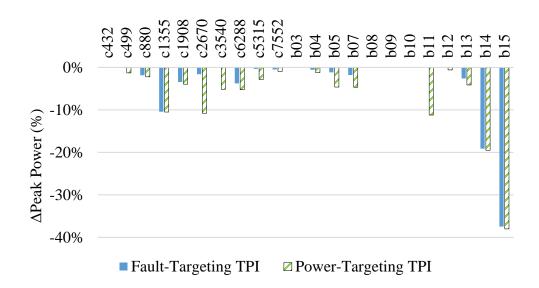

| Figure 7.5: Power-targeting TPI and conventional fault-targeting TPI in peak power comparison.    |  |

|                                                                                                   |  |

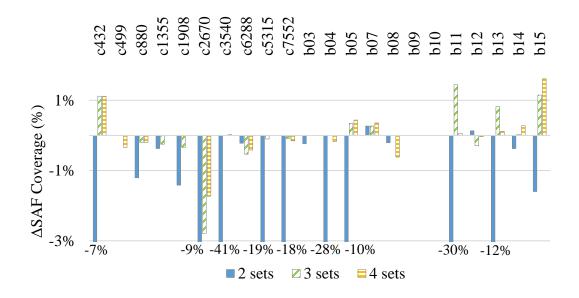

| Figure 7.6: The number of phases impacts SAF coverage substantially                               |  |

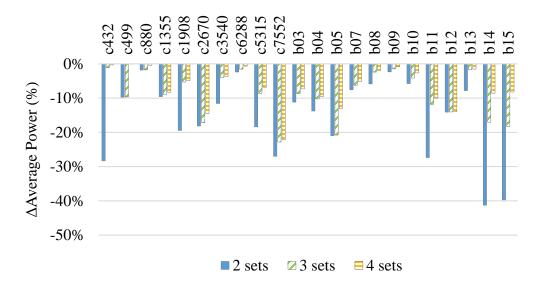

| Figure 7.7: More TPI phases, the benefits to average power degrade                                |  |

|                                                                                                   |  |

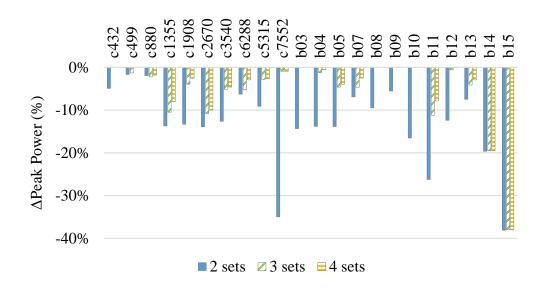

| Figure 7.8: More TPI phases, the benefits to peak power degrade                                   |  |

| Figure 7.8: More TPI phases, the benefits to peak power degrade                                   |  |

|                                                                                                   |  |

| Figure 7.9: The SAF coverage of power-targeting TPI and conventional fault-targeting TPI in three |  |

Figure 7.11: The peak power of power-targeting TPI and conventional fault-targeting TPI in three

| hases75 |

|---------|

|---------|

# List of Tables

| Table 4.1: Training and Evaluation Benchmarks for TPI                                   | 30 |

|-----------------------------------------------------------------------------------------|----|

| Table 4.2: ANN TPI and Conventional TPI Targeting SAF Experimental Results              | 35 |

| Table 5.1: Train Benchmarks for ANN TPI Targeting TDF                                   | 44 |

| Table 5.2: ANN TPI and Conventional TPI Targeting TDF Experimental Results              | 44 |

| Table 6.1: Train Benchmarks for ANN TPI                                                 | 50 |

| Table 6.2: Different sub-circuit size ANN TPI and Conventional TPI Experimental Results | 54 |

| Table 7.1: Power-Targeting TPI Experimental Results                                     | 68 |

# List of Abbreviations

| COP   | Controllability Observability Program                    |

|-------|----------------------------------------------------------|

| CRF   | Cost Reduction Factor                                    |

| DFT   | Design for Test                                          |

| ECO   | Engineering Change Orders                                |

| EDA   | Electronic Design Automation                             |

| LBIST | Logic Built-in Self-Test                                 |

| ML    | Machine Learning                                         |

| MPTI  | Multi-Phase TPI                                          |

| PDF   | Path Delay Fault                                         |

| PRPG  | Pseudorandom Patten Generator                            |

| RPR   | Random Pattern Resistant                                 |

| SAF   | Stuck-at Fault                                           |

| SCOAP | Sandia Controllability/Observability Analysis<br>Program |

| SoC   | System-on-Chip                                           |

| TDF   | Transition Delay Fault                                   |

| TP    | Test Point                                               |

| TPI   | Test Point Insertion                                     |

#### Chapter 1

### Introduction

Modern electronics in critical and high-assurance applications (e.g., self-driving cars, aerospace, and medical devices) have strict reliability requirements. Since defective devices create economic loss or catastrophic loss-of-life, manufacturing tests must be credible in detecting and preventing faulty behavior. To ensure the quality and correct operation of electronic products, tests must be done both during R&D (design verification & classification) and later in production (production/manufacturing testing). *Design-for-test* (DFT) describes the circuit design processes that make sure the required testing is possible to do, and preferably even easy to do.

DFT consists of *integrated circuit* (IC) design techniques that makes testing a chip possible and cost-effective by adding additional circuitry to the chip, adds testability features to a hardware product design to improve the controllability and observability of internal nodes. DFT makes it easier to develop and apply manufacturing tests to the designed hardware. DFT techniques include scan chains and *built-in self-test* (BIST) circuitry.

Logic built-in self-test (LBIST) [1] is a BIST technology in DFT that is commonly used for both manufacturing tests and post-manufacturing reliability checks [2]. LBIST uses on-chip stimulus generators, i.e., *pseudorandom pattern generators* (PRPGs) [3], [4] to stimulate circuit inputs and set circuit states while circuit outputs and states are observed. When complementing conventional test methods, LBIST can significantly increase fault coverage while decreasing test application time. With embedded LBIST, devices become testable with minimal functional interruption by saving the circuit state, applying test enable/disable signals, and then reloading the circuit state to resume the normal function. A major challenge for LBIST is detecting *random pattern resistant* (RPR) faults [5]. RPR faults manifest in logic with many inputs when few input combinations can excite certain logic paths, and therefore pseudo-random tests often fail to excite and observe RPR faults. The prototypical example of an RPR fault is the output of a large logic gate; the probability of the output of a 32-input AND gate being logic-1 and exciting a stuck-at-0 fault at it's output is  $2^{-32}$  (presuming all AND gate inputs are equally likely to be logic-0 or logic-1), which implies more than one billion pseudo-random patterns may be needed to excite the fault. Under the presence of RPR faults, applying LBIST becomes time-consuming and power-intensive, which means test costs increase and circuit reliability degrades.

A method to improve LBIST performance is modifying circuits with *test points* (TPs). TPs change circuit values or observe values in a circuit, thus making the detection of RPR faults easier. *Test point insertion* (TPI) techniques find high-quality TPs locations which improve fault coverage or reduce the required number of test patterns. Using TPs to increase random pattern effectiveness is well established in literature [6]–[8], but TPI methods still strive to improve their computational performance. Since the concept of TPI was proposed by Hayes and Friedman [6] in 1974, numerous algorithms have improved TPI performance by using fault simulation to classify RPR faults and propose TP locations [7] by using *automatic test pattern generation* (ATPG) [9], by using gradient optimizing techniques [8], and by incorporating many other nuances and using a variety of algorithms. All of these methods are less-than-optimal, which is necessary because optimal TP placement is a known computationally-infeasible problem [10]. Therefore, it is imperative to continue exploring TPI methods that select higher-quality TPs with less computational resources, since reduced execution time translates to increased TPI efforts, which in turn translates to higher-quality TPs being inserted into a circuit in a given amount time.

Unfortunately, the computational complexity of the algorithms that implement these techniques increases faster than the increasing size of logic circuits [10]. Since computational resources are in high demand by several *electronic design automation* (EDA) tool users during circuit development, designers must sacrifice testability or other circuit qualities if EDA engineers do not increase algorithm efficiency.

New computing methods, like *artificial neural networks* (ANNs), can increase algorithm efficiency and keep LBIST quality high. ANNs can solve complex problems, like image and speech recognition, and they can significantly increase the quality of existing algorithms while simultaneously decreasing computation time. Recently, ANNs have been applied to several EDA problems with noteworthy success [11], [12], but applying ANNs to DFT problems is in its infancy.

Another major challenge for LBIST is excessive test power. Excessive power not only discourages circuits in portable environments but also causes overheating which degrades performance and reduces chip life. Beyond chip functionality, excessive power during test increases manufacturing costs by requiring more expensive chip packaging or by reducing yield. During wafer test, wafer probes have current limits, and high switching activity during test increases power instability; this instability changes logic states and causes false failures, thus reducing yield. Existing TPI methods may reduce this high switch activity by inserting control TPs, but it may also come at the cost of reduced fault coverage. A new TPI procedure should be explored to reduce test power without affecting test quality, and TPs can be inserted after finding test power issues during silicon bring-up.

This dissertation explores using TPs to improve LBIST performance. Chapter 2 gives a survey on TP architectures and TPI methods and describes TPI methods for different purposes and their weakness. Chapter 3 introduces ANNs' history, structures, training methods and applications.

Chapter 4 and Chapter 5 present the methods of ANNs TPI targeting *stuck-at fault* (SAF) and targeting *transition delay fault* (TDF), respectively, including ANN creation, training and evaluation on SAT/TDF effectiveness and execution time. Chapter 6 futher develops the ANN for TPI, e.g., by exploring ANN input features, output labels, and a more detailed ANN parameters exploration. Chapter 7 demonstrates a procedure of power-targeting TPI with a multi-phase strategy and compares it against conventional fault-targeting TPI on SAF coverage, average power, and peak power.

#### Chapter 2

### Background

# 2.1 **TP** Architectures

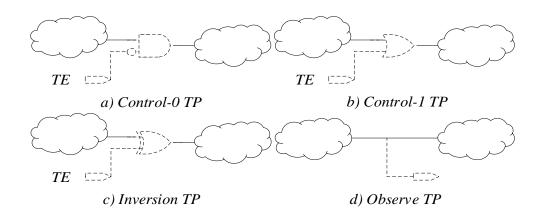

TPs are circuit modifications that change or observe circuit functions during test but do not change the circuit function when disabled [6], [7]. Conventional TPs are categorized into two types [13]: control TPs and observe TPs (as shown in Figure 2.1 (a), (b), and (d)). Control TPs are typically implemented using OR gates for control-1 TPs or AND gates for control-0 TPs (and NAND/NOR gates can be used at the output of inverters) [14]. During test, a test enable pin forces lines to their controlled values [15]. While not under test, this test enable pin is disabled and the circuit function does not change. The goal of control TPs is to increase the probability of exciting faults in a circuit and to make faults easier to observe by creating propagation paths to circuit outputs. Observe TPs change circuit observability by inserting fan-outs to circuit outputs, which makes faulty values on lines easily observed [16].

Figure 2.1: Logic-level implementations of control, inversion, and observe TPs.

The source of test enable and the output for observe points can either be a pin or a scannable latch [14]. Although test enable is most often modeled as a pin, implementing it as a circuit pin is

impractical given the high cost of circuit pins. Instead, additional TP "pins" are typically implemented as the outputs and inputs of scannable latches since a large circuit with many TPs and (latch-implemented) TP pins requires large area overhead. There are numerous articles on reducing TP pin/latch area overhead whilst using TP pins selectively to increase fault coverage, which is surveyed in Section 2.2.

Although effective at increasing SAF coverage, both control and observe TPs have detriments, hence TPI methods must carefully select TP locations and types. Since control TPs force lines to '0' or '1' when active, their controlled line can only be a single value when the TP is active: this prevents one SAF on the line from being excited. Additionally, active control TPs block the transmission of excited faults through the controlled line. Although observe TPs do not block faults like control TPs, osbserve TPs cannot detect RPR faults which are difficult to excite.

In contrast to control TPs, inversion TPs use inversions to change line values during test [17]–[21]. Inversion TPs are made with XOR gates and a test enable pin (shown in Figure 2.1(c)): when the test enable pin is active, the XOR gate becomes an inverter; otherwise the XOR gate acts as a buffer. In contrast to conventional control TPs which force lines to values, inversion TPs invert signal probabilities, i.e., if a line has an 80% probability of being logic-1, the line will have a 20% probability of being logic-1 with an active inversion TP. Because active inversion TPs do not force a single value, both stuck-at-0 and stuck-at-1 faults can be excited on active TP locations. Additionally, faults can propagate through inversion TPs to circuit outputs (unlike control TPs which block faults from propagating through) [21]. However, inversion TPs add more propagation delay, power, and overhead compared to control TPs [21], [22]. Additionally, RPR faults may require values to be forced to optimally increase fault coverage [21] that inversion TPs cannot perform.

# 2.2 TP Selection Architectures

Although TPs can significantly improve fault coverage, they can create significant area overhead, which in turn increases production costs and reduces yields due to larger die areas and fewer dies per wafer [23]. One study found chip area increased by 2.68% when using logic BIST, and TPs constituted 43% of this area increase [24]. It is therefore important to reduce the area overhead of TPs whilst keeping fault coverage high.

To reduce TP area overhead, some methods proposed sharing flip-flops or other existing circuit signals to reduce TP-controlling hardware [13], [17], [24]–[28]. Youssef et al. [13] and Nakao et al. [25] proposed sharing a single flip-flop for multiple test enable signals, which reduced the number of flip-flops that were required to implement control points. Yang et al. [24], [27] found more than half of TPs inserted were control points, so replacing dedicated test enable flipflops with existing functional flip-flops reduced area overhead: suitable functional flip-flops could be found in each TP's fan-in region with a short distance from the control TP. Additionally, the test enable signals were only active in the test mode since the test enable signal was generated based on latch value combinations that could never occur in the functional mode, i.e., unused states of a finite state machine. Muradali et al. [26] proposed a self-drive TP that used test enable signals created from gate outputs already existing in the circuit, which eliminated the test enable signal generation. Similar to [26], [17] used pre-existing signals for test enable without the need for extra registers. Chang et al. [28] used controllability don't-cares to generate TP activation signals instead of a global test enable signal, which generated test enable signals locally and allowed TPs to be randomly activated: these controllability don't-cares were constant values in functional mode (i.e., circuit states which were accessible only through scan) and thus could only change values in test modes.

Other studies proposed reducing the number of TPs needed through various means. Basturkmen et al. [29], Tamarapalli et al. [30] partitioned circuit tests into multiple phases, and sub-sets of control TPs were activated during certain phases. This provided greater control over the interaction between control TPs and helped reduce the total number of TPs needed to obtain adequate fault coverage.

# 2.3 TPI Algorithms

TPI algorithms iteratively select TPs amongst a list of TP candidates: each iteration, the TP which increases the fault coverage the most whilst not violating other constraints (e.g., fault coverage, power, delay, etc.) is selected. Optimal TP placement in circuits with reconvergent fanouts is a known NP-hard problem [31], [32], thus most TPI approaches use heuristics to select TP locations, i.e., solve problem in a faster way by sacrificing optimality and accuracy.

Many TPI algorithms have been proposed in literature, and most algorithms performed the following steps to insert a single TP. First, fault simulation or approximate testability measured identified RPR faults. Second, candidate TPs were evaluated for their impact on fault coverage. Third, the TP with the highest positive impact on fault coverage was inserted into the circuit. This process was repeated until the number of desired TPs was inserted or the estimated fault coverage reached a pre-designated limit.

# 2.3.1 TPI Computational Difficulties

The challenge of TPI is placing the fewest number of TPs while maximizing fault coverage. Each TP requires logic circuitry, which in turn creates undesirable overheads: static and dynamic power, delay, and non-functional circuit area. Designers typically allocate budgets to TPs (and other DFT hardware), thus TPs must increase fault coverage to acceptable levels under these budgets. Selecting optimal TP locations (and many other DFT problems) is a known NP-hard problem [32], thus existing TPI methods relied on heuristic approaches to select TP locations. Inserting *T* TPs into a circuit among *T'* candidate TPs creates C(T', T) possible TP choices and finding the fault coverage impact of a choice requires computationally-intensive fault simulation. TPI heuristics address this by replacing fault simulation with less accurate fault coverage estimations [33], [34] and using greedy-algorithm approaches. The most common approach is iterative [33], [21] and [35]: the algorithm evaluates candidate TPs one at a time to find the one which one increases fault coverage the most, inserts it, and repeats this process until no more TPs are desired or needed.

Unfortunately, the computational complexity of iterative TPI grows faster than available computing resources. To insert a single TP, iterative TPI algorithms require evaluating every candidate TP, and the number of candidate TPs in a circuit is proportional to the size of the circuit (i.e., one or more candidate TPs can exist on every circuit line). Additionally, the complexity of TP-evaluating heuristics is linearly proportional to circuit size, and as circuit sizes increase, more TPs are needed to increase a circuit's fault coverage to acceptable levels, presumably at a rate linearly proportional to the circuit size (i.e., if the circuit size is doubled, meeting fault coverage goals requires twice as many TPs). Therefore, if circuit size grows by *S*, TPI complexity grows by  $S \cdot T \cdot T'$ . Presuming computer speeds increase with circuit complexity (i.e., algorithm performance increases at a rate of *C*), TPI time will grow at a rate of  $S \cdot T \cdot T'/S = T \cdot T'$ .

# 2.3.2 TPI Using Simulation

Using fault simulation to find undetected faults and then inserting TPs to detect these faults is a straightforward method of TPI. Iyngar et al. [36] inserted control TPs on gate outputs where faults were not excited while inserting observe TPs at the input of gates which blocked propagation. Touba et al. [10] used backward path tracing to identify sensitized paths from undetected faults and selected a set of TPs for enabling the undetected faults to be detected. Ramakrishnan et al. [37], Menon et al. [38] used control TPs on undetected fault sites to sensitize a path to undetected faults in sequential circuit.

Several methods [29], [30] used probabilistic fault simulation to guide TP placement combined with greedy heuristics. Probabilistic fault simulation performed regular logic simulation to find signal probabilities and faults that were propagated in the circuit, and then used these probabilities to predict the probability any fault would be detected at a given location [30]. Tamarapalli et al. [30] used this method combined with a divide-and-conquer technique: probabilistic fault simulation was performed in phases, and at the end of each phase, TPs were inserted to target faults with the lowest detection probability. Basturkmen et al. [29] improved memory usage and TPI CPU time whilst marginally sacrificing TPI accuracy: instead of using logic simulation to determine all faults which could be detected on each circuit line (and the probability of each fault being detected), a representative of all faults at each fan-out location was chosen in order to reduce the number of faults to consider during TPI.

#### **2.3.3 TPI Using Approximate Testability Measures**

Fault simulation accurately quantifies fault coverage, but its computation complexity (in terms of CPU time and memory) is infeasible for modern circuits: to overcome this, numerous studies replace fault simulation with approximate testability measures, such as the *Sandia Controllability/Observability Analysis Program* (SCOAP) [39] and the *Controllability Observability Program* (COP) [40]. SCOAP is a linear complexity algorithm (relative to the number of logic gates in a circuit to analyze) which estimates the number of circuit inputs needed to force a logic-0/1 on a line, i.e., the *Controllability (CC)*. Using these values, SCOAP can then

estimate the *Observability* (*CO*) of a line, which is the number of inputs that must be set to propagate a faulty value on a line to an observable output. SCOAP also includes the depth of a line in its controllability and observability estimations. Alternatively, COP predicts the probability a line will be logic-0/1 and the probability a line's value will be observed at a circuit output presuming random stimuli is applied to circuit inputs. COP values can directly be used to predict the probability of a fault being detected: *CC* \* *CO* for stuck-at-0 faults and *CC* \* (1 – *CO*) for stuck-at-1 faults, i.e., the probability a line is excited to the line's value is observed at a circuit output. Controllability and observability measures can therefore be used to identify hard-to-control and hard-to-observe locations in a circuit, and they can be used to predict the current fault coverage (with or without a TP) of a circuit without performing fault simulation. TPs can then be inserted based on this information.

Compared against exact fault simulation, testability measurements take substantially less time to calculate but lose accuracy for circuits with many reconvergent fanouts. However, experiments have suggested approximate testability measurements can be accurate enough for use in TPI for large designs [41]. Therefore, many TPI methods from literature [33], [41]–[45] used a cost function to estimate a TP's quality, with a typical example [42] provided below: *F* is a set of faults, and  $P_{d_i}$  is the probability the fault *j* is detected (calculated using COP).

$$U = \frac{1}{|F|} \sum_{\forall j \in F} \frac{1}{P_{d_j}}, P_{d_j} = \begin{cases} CC * CO, for stuck - at - 1 fault\\ CC * (1 - CO), for stuck - at - 0 fault \end{cases}$$

2.1

Cost functions, such as U, are used as indicators of circuit testability, and many TPI algorithms attempt to maximize such cost functions during TPI. In this example, the value of U changes when a TP is inserted, and the difference in U before and after a TP is inserted is called the *actual cost reduction* (ACR) [42]. Gradient calculations [42] can select TPs with the largest ACR, but the computational complexity of finding the ACR for every TP is too high and

unpractical for modern circuits [41]. Therefore, the concept of a *cost reduction factor* (CRF) is introduced to approximate ACRs [45]. The algorithms which use CRFs and ACRs typically perform as follows: first, controllability and observability are calculated using an approximate testability measure, e.g. COP or SCOAP; second, the CRF/ACR for each TP in a set of candidate TPs is calculated, and TPs with a CRF/ACR below a given threshold are discarded; third, the ACR for remaining candidate TPs is calculated; lastly, the TP with the largest CRF/ACR is inserted.

When using a cost function to evaluate TPs, studies added nuances to select superior TPs or to reduce TPI CPU time. Bist et al. [43] selected TPs whose impact on timing slack and fault coverage were smaller and larger than a given threshold, respectively. Both Tsai et al. [41] and Bist et al. [33] proposed a hybrid cost reduction: after a TP was inserted, only faults with a large change in  $1/P_{d_f}$  had their  $1/P_{d_f}$  value recalculated using fault simulation (with other faults being calculated with testability analysis); the rational for this was the large changes in a CRF may be inaccurate. Nakao et al. [44] proposed three strategies for accelerating CRF-based algorithms: they removed TPs with redundant TPI-effective regions (i.e., regions where the same controllability (for control TPs) or observability (for observe TPs) were changed, chose the TP with the highest CRF (i.e., did not calculate an ACR), and reduced candidate TPs by selecting the first TP found to reduce the cost function (instead of calculating the ACR or CRF for all candidate TPs).

Beyond COP and SCOAP, other methods used additional/alternative cost functions or introduce additional constraints. Youssef et al. [13] and Gerstendörfer et al. [46] identified RPR faults using COP and created fault sectors: RPR faults were sorted by ascending logic levels, then control TPs targeted faults in ascending order and observation TPs targeted faults in descending order; this prevented the same fault being targeted by the same TP, which reduced the number of TPs required. Gerstendörfer et al. [46] used *test counts* (TCs) to complement COP-based TPI: the TC of a line was the fewest number of tests that must pass through the line such that all faults in its fan-in cone would be tested, and TPs were selected in order of the most tests that must pass through the TP location. Geuzebroek et al. [8] proposed several cost functions using one or multiple test analysis measurements (COP, SCOAP, or TC): TPI was split into multiple stages, where each stage selected a cost function to target the current hardest test problem, i.e., detecting RPR faults, reducing test vectors, or a combination of the two. He et al. [47] [48] used an efficiency equation for TPs that evaluated the size of a TP fan-out/fan-in cone-of-influence and the number of undetected faults in this cone, which in turn was used to pick the TP with the highest efficiency. An estimation metric was then used to approximate the final area overhead and test coverage without TP insertion and synthesis. Chen et al. [49] proposed a new conditional testability measure to overcome COP's inability to account for reconverging fan-outs, thus increasing the accuracy of calculated cost functions.

Many methods incorporated non-fault coverage information (e.g., timing violations) into their cost functions [43] or efficiency equations [48], which are further discussed in the following sections.

#### **2.3.4 TPI Using Multiple Measures**

Some approaches utilized both fault simulation and testability measures to increase TP quality [50]–[52]. Sethuram et al. [50] reduced test vector counts and test generation time by considering layout and timing information for observe TPs. The cost function of an observe TP was the product of the total number of independent faults (i.e., faults which cannot be simultaneously detected by any single pattern) in the fan-in cone of the observe TP (which was found through fault simulation) and the minimum number of controlled primary inputs needed to propagate the independent faults to the TP location (estimated using SCOAP). Acero et al. [51]

and Moghaddam et al. [52] performed COP and fault simulation to calculate fault testability, propagated faults, and faults blocked by control TPs: a control TP cost function was composed of the controllability of blocked faults, and the cost function of observation TPs composed of observability of unobserved faults.

# 2.4 Modern Targets for TPI

Modern TPI not only targets increasing SAF coverage, but also considers extra constraints imposed by modern technologies, e.g., increasing delay fault coverage, reducing test power, reducing timing impacts. These constraints make TP selection much more difficult than before, but addressing them improves circuit performance [14].

# 2.4.1 Path Manipulation to Increase Path Delay Fault Coverage

A *path delay fault* (PDF) [53] occurs when any path's delay exceeds a circuit's designed clock speed, and PDFs model defects that cause cumulative propagation delays along a circuit path that exceed the circuit's specifications. Unlike SAFs, PDFs are defined by their environment: a PDF exists only within a certain range of operational clock speeds. PDFs are tested using a set-up vector to create the preconditions for a transition, and a second trigger vector to initiate the transition. Using specialized test hardware, a clock period greater than the operational clock period can be used to create the set-up vector and to apply the trigger vector, but the operational clock period must be applied after the trigger vector to properly capture a slow transition along a path. If the target output has not changed from its value after the set-up vector, then the circuit is faulty.

There are three problems associated with PDFs, which are problems TPs have attempted to address. First, the number of paths (and number of PDFs) in practically-sized circuits is too large for test tools to handle [54]. Second, the number of tests needed to detect all PDFs is too large [55]. Third, many PDFs in practical circuits are not testable [56]. To remedy this, TPs can divide full paths into sub-paths, thus making paths easier to test and reducing the number of paths [57]. Additionally, it is easier to generate tests for shorter sub-paths compared to full-sized paths [57].

TPI methods have incorporated these observations into cost functions that represent the number of paths in a circuit (i.e., the TP that reduces the total number of paths in the circuit is iteratively chosen) [57]–[59]. Pomeranz et al. [58] used test point to divide the set of paths into a subset paths and reduce the number of paths to be tested.directly. Tragoudas et al. [57] added an additional constraint to the above cost function, i.e., the clock speed of the circuit under test: if a TP reduced the longest path in the circuit, the clock speed during test could be increased, thus decreasing test application time. Uppduri et al. [59] targeted non-robust-dependent faults (faults in functionally sensitize paths) [60], which reduced the fault set, thus reducing the number of TPs.

#### 2.4.2 Test Power Reduction

The power consumption of digital systems is considerably higher in a test mode compared to functional modes. This is because during normal circuit operation, a relatively small number of flip-flops change their value each clock cycle, whilst in a test mode, a much larger number of flip-flops will change values, which results in excessive switching activity and current spikes [61]. Especially during self-test, power dissipation increases since random patterns desire as many nodes switching as possible so as to test for many faults [62]. If the peak power during test is too large, there will be a  $V_{dd}$  drop or ground bounce that can cause false-failures or device damage.

Some studies [61], [62] inserted TPs to reduce power consumption during test, but TP placement was restricted to flip-flop outputs. Gerstendörfer et al. [62] used modified shift registers that suppress activity at the output during shift operations: by adding NOR or NAND gates to the outputs of latches controlled by a test enable pin, latch outputs were forced to known values and

thus did not cause circuit switching. Sankaralingam et al. [61] proposed inserting TPs into a conventional full-scan circuit to keep peak power during scan below a given limit without decreasing fault coverage (with TPs being inactive during the capture cycles): a subset of scannable flip-flop outputs were forced to 0 and 1 during scan. First, cycle-by-cycle simulation identified which scan cycle's power consumption was greater than the specified limit. Second, an event-driven, selective trace simulation procedure [63] estimated the power reduction for every latch when its output was forced to 0 or 1, then latches were iteratively forced to reduce power consumption.

# 2.4.3 Timing Impacts of TPs

Timing is fundamental to modern digital electronics, as it provides synchronization that is necessary for error-free data transfer. Data must be stable before and after the clock edge to be reliably transferred. If not properly synchronized, there will be a host of design issues like, including timing hazards, metastability, and race conditions.

Inserted TPs may cause circuit timing violations that break proper circuit operation [23], and resolving these timing violations may require several tedious design iterations. Many attempts have been proposed [43], [64]–[66] to insert TPs to increase fault coverage without creating new timing violations. In Bist et al. [43] and Vranken et al. [66], timing analysis was performed before TPI to identify paths with small timing slacks, then TPI was performed after removing candidate TPs that reside on such paths. Tofte et al. [64] performed TPI without any constraints, then timing analysis was performed to remove TPs which caused timing violations. Roy et al. [65] performed TPI at the RTL-level (instead of the typical logical netlist level), which meant TPs were inserted before logic synthesis, which avoided later design iterations.

#### Chapter 3

#### Introduction to ANNs

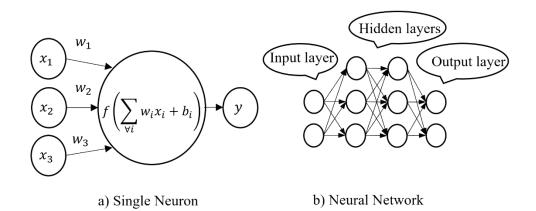

Inspired by biological neural networks, ANNs are computing systems consisting of an extremely large number of simple processes (hardware processors, software functions, etc.) with many interconnections. ANNs are one type of model for *machine learning* (ML) and attempt to use the same principles of human thinking. Nodes in ANNs are artificial neurons that are computational models inspired by natural neurons [67]. Since the great potential of ANNs is high-speed processing provided in a massive parallel implementation, they are used in many fields [68]. ANNS are widely used in engineering: they are used as models of biological nervous system and "intelligence", as real-time adaptive signal processors, as controllers implemented in hardware in robots, and as data analytic tools [69].

### 3.1 ANNs history

ANNs were a hot topic in artificial intelligence starting in the 1940s. Warren McCulloch and Walter Pitts opened the subject by creating a computational model for neural networks in the early 1940s [70]. Hebb was the first to define a learning rule to explain the behavior of networks of neurons in 1949 [71]. In the late 1950s, Rosenblatt developed the first perceptron learning algorithm [72]. In 1973, Dreyfus used backpropagation to adapt ANN parameters proportion to error gradients [73]. In 1992, max-polling was introduced to help improve ANN quality [74].

## **3.2 ANNs structures**

Many ANN structures exist in literature, and Figure 3.1 illustrates the prototypical ANN structure. ANN architectures comprise an input layer, hidden layer(s), and an output layer. The input layer receives the input values and the output layer stores output values. Layers between the input and output layer are hidden layers, to which there can be a single or multiple layters. Each

layer can have one or more neurons. Connections between neurons have weights and biases. Neurons have activation functions that determine a neuron's input given its inputs. Many choices exist for neuron activation functions and neuron arrangements (the number of levels, neurons per level, etc.), and these hyperparameters are best optimized through trial-and-error.

Figure 3.1: An example of a) a single neuron, and b) the ANN prototypical structure

# 3.2.1 Neurons

ANNs are composed of artificial neurons similar to biological neurons. The input neurons collect feature values of the problem to solve, such as the pixels in images or letters in documents, or their inputs can be from the outputs of other neurons. The outputs of the final neurons return an answer to the problem, such as recognizing an object in an image.

# 3.2.2 Connections

ANNs consist of connections, with each connection providing the output of one neuron as an input to another neuron. Each connection has a weight (noted as  $w_i$  in Figure 3.1) and bias (noted as  $b_i$  in Figure 3.1) assigned to it, and these weights represent its relative importance [75]. A given neuron can have multiple inputs and single output connection.

#### 3.2.3 Activation Functions

Activation functions are mathematical equations that determine the output of a neural network. The function is attached to each neuron in the network and determines its output value. Activation functions also normalize the output of each neuron to a range between 1 and 0 or between -1 and 1. Activation functions can be divided into linear and nonlinear (e.g., Sigmoid, Tanh, Rectified Linear Unit (ReLU), or Softmax) [76].

### 3.3 Training ANNs

Once a network has been structured for a particular application, that network is ready to be trained. To start this process the initial weights are chosen randomly. Then, the training (or learning) begins. There are two approaches to training – supervised and unsupervised. In supervised training, training provides a set of both sample problem inputs and desired problem outputs. The network then processes the inputs and compares its resulting outputs against the desired outputs. Errors are then propagated back through the system, causing the system to adjust the weights that control the network. In unsupervised training, the network is provided with inputs but not with desired outputs, and the training algorithm attempts to find trends in the data to apply to future possible inputs.

### **3.4 ANN applications**

ANNs have been widely applied to real-world problems in business, engineering, language, and practical consumer products. In business, ANNs were used for credit scoring [77], financial analysis [78], stock performance prediction [79], etc. In engineering, ANNs were implied in aircraft component fault detectors [80], automotive guidance systems [81], robotics control system [82], etc. ANNs were utilized in language, e.g., in email classification and categorization [83], named entity recognition [84], machine translation [85], etc.

ANNs also have many applications in the electronics field, including chip failure analysis [86], circuit chip layouts [87], prediction of electronic structure properties [88], etc. ANNs have also been used in DFT testing problems, e.g., scan-chain diagnostic [11], fault classifiers [12], and test pattern generation [89], [90].

#### Chapter 4

# ANNs TPI Targeting Stuck-at Fault Coverage

This chapter introduces a method of applying ANNs to TPI for increasing SAF coverage while drastically decrease CPU runtime. Increasing TPI quality is essential for the modern logic circuit; the computational requirements of current TPI heuristics scale unfavorably against increasing circuit complexity and it is time consuming process. ANNs were applied to several EDA problems with noteworthy success [35], [11]. This gives the motivation to explore ANN to increase TPI algorithm efficiency and overcome the drawbacks of TPI heuristics.

Much of this chapter has been published by the author in [91].

#### 4.1 Introduction to the Stuck-at Fault Model

A SAF is a particular fault model used by fault simulators to mimic a manufacturing defect within an integrated circuit. When a line is stuck it is called a fault: individual line is assumed to be stuck at logical '1' or '0', called stuck-at-1 fault and stuck-at-0 fault, respectively. A single stuck line is a fault model used in manufacturing testing; the model assumes that only one input or output on one gate will be stuck at logic-1 or logic-0 at a time. SAF coverage represents the percentage of all possible SAFs that a given test will detect. To test a SAF, a test vector applied to the circuit's inputs must have at least one output pin different from fault-free outputs [92].

# 4.2 Proposed Method

The proposed method created an ANN that evaluated TPs using circuit probability information, i.e., COP controllability and observability values [40], which many other TPI methods ([33], [21] and [35]) used. Evaluating a single TP did not require re-calculating COP values: this was a noteworthy advantage of the ANN over TP-evaluating heuristics that required re-calculating values when evaluating a TP: calculating COP values for a circuit with G gates

requires O(G) time. By performing COP once per TP insertion as opposed to once per TP evaluation, this reduced TP evaluation time from O(G) to O(1), which reduced the time to select a single TP from  $O(T' \cdot G)$  to O(T'). However, for ANN TPI, long training time might negate this benefit, thus the overall effect on TPI time (with and without training) was explored in Section 4.8.1.

The proposed ANN evaluated TPs and could be used in any iterative TPI algorithm [33], [21] and [93]. Every iteration, the algorithm evaluated each individual TP to find the "best" TP (i.e., the TP which increased SAF fault coverage the most), and the algorithm inserted this TP into the circuit. This iterative selection and TP insertion continued until (1) the number of TPs inserted reached a pre-designated limit (representing hardware overhead), (2) the predicted fault coverage reached a pre-designated limit (i.e., no more TPs are necessary), (3) no TPs were predicted to increase fault coverage, or 4) a CPU time limit was reached.

# 4.3 ANN Input

The input features to the ANN TPI were circuit *CC* and *CO* values. These were the same values used by other conventional TPI algorithms [40], but the ANN used only pre-TP activation values. Using these values in such a manner presented several potential benefits. First, using only pre-TP activation values forgone the need to re-calculate *CC* and *CO* values for every TP and decreased TP evaluating time. This benefit could also be interpreted as allowing for more (or alternate) TPs to be inserted with identical computational effort, which in turn allowed for increased TP selection quality. Second, an ANN could find relations between values during training which heuristic algorithms may not take advantage of. For instance, the known issue of *CC* and *CO* values not considering fan-outs was ignored by many TPI algorithms, but a trained ANN could find and acted on such nuances automatically.

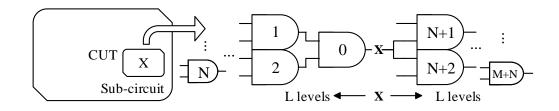

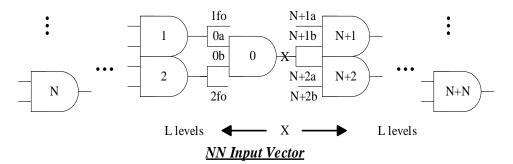

In contrast to conventional TP-evaluating heuristics, the ANN performed its evaluation on a transformed sub-circuit centered around a candidate TP location as opposed to estimating a TP's impact on the entire circuit. This was a consequence of using ANNs: the input size of an ANN must be of a pre-determined size, whereas logic circuits could be of any size and topology. In theory, the ANN could handle the largest possible circuit size or smaller by giving "unused" ANN inputs "default" values, but this required an infeasibly large ANN that is impossible to train. Instead, the ANN analyzed features around a TP's location by analyzing a sub-circuit L levels forwards and backwards of the indicated location, as Figure 4.1 illustrates.

Figure 4.1: A sub-circuit size is represented by *L* levels. "X" marks the TP location.

The use of a sub-circuit presented a potential detriment of the ANN to explore: the ANN used less information for its TP-evaluating calculations and may return less accurate qualifications. The ANN would be as accurate as a heuristic or more using identical input features only if L is large enough to capture the entire circuit, but this created an infeasibly large ANN that was impossible to train. Section 6.3.2 explores whether analyzing sub-circuits decreases the ANN's performance compared to conventional TPI.

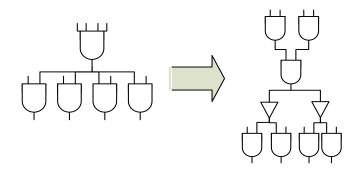

A nuance of the sub-circuits was they must have a particular circuit configuration (hence "transformed" in transformed sub-circuits): every gate must have at most two inputs and two fanouts. So circuits had to be converted into a consistent fan-in/out structure before the ANN was used and trained. Any given circuit could be converted to this structure by replacing gates with more than two inputs with functionally equivalent copies and by adding buffers to fan-outs, as is illustrated in Figure 4.2. After conversion, the circuit's logic function was not changed, and *CC* and *CO* values for lines and gates in the original circuit were same.

Figure 4.2: A conversion of a sub-circuit to the format of no more than two fan-in/fan-out per gate.

The input vector to the ANN was *CC* and *CO* values around a candidate TP location in a vectorized format, as is illustrated in Figure 4.3. The first value was the *CC* value of the candidate TP location. This was followed by the *CC* value of gate inputs (and fan-outs) feeding the TP location, then the *CC* value of gate inputs (and fan-outs) feeding these gates, etc., in a breadth-first order. This was repeated until *L* levels values were collected. This process was repeated starting at the candidate TP location moving forward in the circuit until *L* levels values were collected. When moving forward, the values of fan-ins to gates were also captured. *CC* values were followed with *CO* values in the same order. For gates with one input or one fan-out, "default values" replaced the values in the feature string: non-existent lines had 50% controllability and 0% observability, and non-existent gates, which were normally represented using a one-hot encoding (e.g., 0001 = AND, 0010 = OR, etc.), were replaced with a no-hot encoding (e.g., 0000).

$CC_{0}, CC_{1fo}, CC_{0a}, CC_{0b}, CC_{2fo}, CC_{1}, CC_{2}, ..., CC_{Nb}, CC_{N+1a}, CC_{N+1b}, ..., CC_{N+N-1}, CC_{N+N}, CO_{0}, CO_{1fo}, CO_{0a}, CO_{0b}, CO_{2fo}, CO_{1}, CO_{2}, ..., CO_{Nb}, CO_{N+1a}, CO_{N+1b}, ..., CO_{N+N-1}, CO_{N+N}, Gate 0, Gate 1, Gate 2, ..., Gate N, Gate N+1, Gate N+2, ..., Gate N+N$

Figure 4.3: The ANN input features are CC, CO, Gate type.

#### 4.4 Output Label

The output of the ANN was the impact on SAF coverage, a TP had on a circuit when it was inserted and activated:  $\Delta FC_t = FC - FC_t$ . In this formula, *FC* was fault coverage of sub-circuit with no TPs, and *FC<sub>t</sub>* was fault coverage of sub-circuit with TP *t* active. Training values were found through fault simulation of a circuit before and after a TP had been inserted. This was a relatively computationally intensive process to perform, but every time it was performed more training data would be generated and the accuracy of the ANN would increase. To avoid the ANN being too specialized to one type of circuit, fault-simulated TP impacts were calculated for a diverse set of circuits.

# 4.5 Training Data Generation

The data generation process included generating input features and corresponding labels required to train the ANN. First, arbitrary locations were chosen in training circuits and subcircuits were extracted from these locations. Second, *CC* and *CO* values (which require a singlepass calculation per training circuit to generate) and gate types (AND, NOR, etc.) in the sub-circuit were recorded. The output label was generated by fault simulation, which was computationally demanding: fault simulating *V* vectors in a circuit with *G* gates and *F* faults requires  $O(V \cdot G \cdot F)$  time, therefore collecting *S* training samples required  $O(S \cdot V \cdot G \cdot F)$  time. Reducing *V* to a small number of vectors was not an option, since an LBIST test typically applied many vectors. To generate training output faster, two speed up techniques were used to reduce time.

The first training speedup technique was to apply fault simulation to sub-circuits in lieu of larger circuits with assistance from circuit probability information. Performing fault simulation on sub-circuits significantly reduced *G* and *F* (since the number of faults in a sub-circuit was proportional to the number of gates), which in turn reduced fault simulation time. However, truly random stimulus of sub-circuit inputs and direct observation of sub-circuit outputs was not realistic: under random circuit stimulus, sub-circuit inputs were not truly random, nor are sub-circuit outputs always observed. To account for this, the training data generation program calculated COP controllability and observability values once per training circuit. This additional O(C) calculation time was negligible when taking a significant number of sub-circuit samples from a given circuit. Fault simulation weighted each sub-circuit input vector using these COP controllability values. Additionally, if a fault's effect reached a sub-circuit output, fault simulation probabilistically detected it using the COP observability values of sub-circuit outputs.

A second technique reduced training data generation time by eliminating redundant vectors. Simulating all  $2^{|I_S|}$  input patterns (where  $|I_S|$  was the number of inputs of the sub-circuit) for a sub-circuit took significantly less time compared to simulating 10K (or other common pseudo-random test lengths) random patterns for fault simulation for practical values of  $|I_S|$ , but even under many random vectors, all  $2^{|I_S|}$  input patterns may not be applied. This was because the *CC*, *CO* values of inputs can prevent all patterns being applied, even when the number of patterns applied was significantly greater than  $2^{|I_S|}$ . The probability of generating an input pattern based on *CC* and *CO* could be calculated as  $p = \prod_{\forall i \in I} CC'_i$ , where  $CC'_i$  is  $1 - CC_i$  if a 0-value was needed or  $CC_i$  was a 1-value is needed. The probability of generating a pattern in *V* vectors was  $P_i = 1 - (1 - p)^V$ . Likewise, if a fault was observed on an output "o", the probability of the fault being observed on the pin in *V* vectors was  $P_o = 1 - (1 - CO_o)^V$ . By calculating these probabilities, every  $2^{|I_S|}$  input vector was simulated at most once with probability  $P_i$ , and if the vector was applied, simulated faults would be considered detected with probability  $P_o$ .

## 4.6 Training

To make the ANN training process simpler, three separate, smaller ANNs were trained representing the three TP types: control-0, control-1, and observe TPs. The alternative to this was to have a single ANN with an extra "TP type" input, but this made the complexity of the ANN unnecessarily large. When evaluating a TP's quality, the appropriate trained ANN was used.

After training data was created, ANN training was performed under various ANN hyperparameters to minimize ANN error (in this study, mean squared error). Finding a truly optimal ANN for a given training data set is an NP-hard problem [94], and small changes in initial training conditions and ANN parameters can have significant impacts on the resulting ANN quality, thus a trial-and-error process was used to minimize this ANN error.

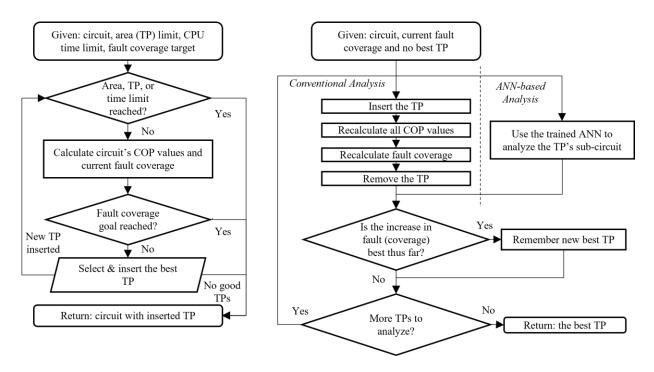

## 4.7 ANN TPI Flow

The use of a trained ANN in a TPI algorithm is analogous to the use of a TP-evaluating heuristic in an iterative TPI algorithm [33]. A trained ANN calculates a candidate TP's quality, and after doing so for every candidate TP, the highest quality TP is inserted. The entire TPI flow is shown in Figure 4.4.

a) Iterative TPI b) TP evaluation (conventional vs ANN-based)

# 4.8 Experiment Results

#### 4.8.1 Experiment Setup

Industry-representative workstations performed fault simulation and TPI using original software. These workstations used Intel i7-8700 processors and possess 8 GBs of RAM, and all software was written in C++ and compiled using the MSVC++14.15 compiler with maximum optimization parameters. Original software was used in lieu of industry tools to obtain a fair comparison of the proposed ANNs against methods from literature: only code which analyzed the "quality" of a TP was changed between the methods thereby minimizing other sources of CPU time differences.

The ANN was trained by Python and TensorFlow. TensorFlow is an open-source symbolic math library developed by Google Brain [95], and it can be used across a range of tasks but has a

particular focus on training and evaluation deep neural networks. TensorFlow provides the TensorBoard function that stores statistical data and plots scalar figures for the training process.

The conventional TPI method used for comparison was from [33]. It [33] is an iterative TPI method that is representative of TPI implemented in industry, although industrial tools have many additional computation-time optimizations. Conveniently, the studied ANNs can directly replace the "quality" measuring subroutine in [33], which eliminated other sources of fault coverage and CPU time differences.

The benchmarks used in this study, both for ANN training and TPI evaluating, are given in Table 4.1, which were from the ISCAS'85 [96] and ITC'99 [97] benchmarks, which represent a wide range of industry-representative circuits. Table 4.1 provides the number of nets in each benchmark ("Num. nets") and the number of nets in the circuit after it was expanded ("Num. exp. nets") using the method resented in Section 4.3. If the benchmark was used for ANN training, the number of training TPs and sub-circuits extracted is given. From each sample/sub-circuit, the impact of a control-0, control-1, and observe TP was fault simulated using the method presented in Section 4.4. The total number of training samples/sub-circuits collected was 11,561.

|            | Benchmarks | Num. nets | Number. Exp. nets | Num. Samples |  |  |

|------------|------------|-----------|-------------------|--------------|--|--|

|            | c17        | 11        | 11                | 2            |  |  |

|            | c499       | 243       | 425               | 6            |  |  |

|            | c1355      | 587       | 881               | 13           |  |  |

|            | c1238      | 543       | 1016              | 14           |  |  |

|            | c2670      | 1426      | 1969              | 25           |  |  |

|            | c6288      | 2448      | 3376              | 52           |  |  |

|            | c7552      | 3719      | 5482              | 72           |  |  |

|            | b02        | 27        | 46                | 2            |  |  |

|            | b04        | 729       | 1221              | 16           |  |  |

| Training   | b06        | 50        | 93                | 2            |  |  |

| aini       | b08        | 179       | 304               | 4            |  |  |

| Tra        | b10        | 200       | 342               | 5            |  |  |

|            | b12        | 1070      | 1900              | 26           |  |  |

|            | b14        | 10044     | 17719             | 242          |  |  |

|            | b15        | 8852      | 16920             | 232          |  |  |

|            | b17        | 32229     | 59818             | 817          |  |  |

|            | b18        | 114598    | 201844            | 2758         |  |  |

|            | b19        | 231290    | 405924            | 5549         |  |  |

|            | b20        | 20204     | 35993             | 491          |  |  |

|            | b21        | 20549     | 36916             | 503          |  |  |

|            | b22        | 29929     | 53564             | 730          |  |  |

|            | c432       | 196       | 310               |              |  |  |

|            | c880       | 443       | 682               |              |  |  |

|            | c1196      | 561       | 978               |              |  |  |

|            | c1908      | 913       | 1315              |              |  |  |

| u          | c3540      | 1719      | 2693              |              |  |  |

| Evaluation | c5315      | 2485      | 4396              |              |  |  |

| lua        | b01        | 47        | 80                |              |  |  |

| Eva        | b03        | 156       | 268               |              |  |  |

| Н          | b05        | 962       | 1783              |              |  |  |

|            | b07        | 433       | 706               |              |  |  |

|            | b09        | 169       | 280               |              |  |  |

|            | b11        | 764       | 1271              |              |  |  |

|            | b13        | 352       | 543               |              |  |  |

Table 4.1: Training and Evaluation Benchmarks for TPI

# 4.8.1 ANN Training Experiments

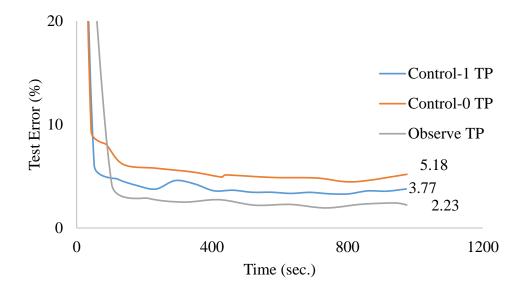

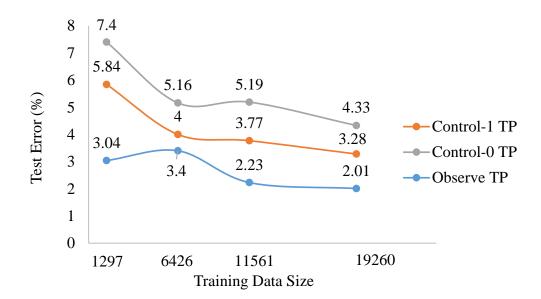

The first issue explored through ANN training was the impact of different ANN structures. As discussed in Section 3.2, many different parameters influence the quality of an ANN, including ANN size (the number of neurons and the number of layers), ANN connectivity, training time, and neuron activation functions. These parameters were thoroughly explored through several parameter sweeps to find the configuration which minimizes the average error of the ANN. Figure 4.5 shows three trends of the control-1 TP, control-0 TP, and observe TP evaluation ANN. The figure shows the ANN accuracy as more training time was allocated, which shows that training effort was "saturated" after some point. All ANNs in this study were trained beyond this saturation point.

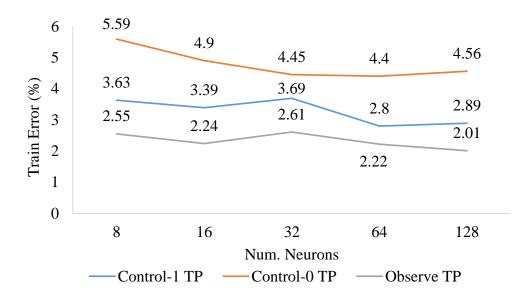

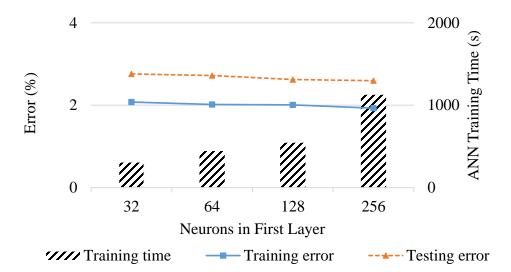

The second issue explored was the neuron's number impact on ANN accuracy. Figure 4.6 shows the accuracy of different ANNs for varying numbers of neurons, which shows more neurons may not produce a higher quality ANN. ANNs with different numbers of neurons (8,16,32,64,128) were used to train control-1 TP, control-0 TP and observe TP in the same literation, and the training error showed the ANN accuracy. The final parameters chosen were two hidden layers with 128 neurons in the first layer and a single neuron in the second layer. A ReLU activation function and the Adam Optimization method [98] were used for training the ANN.

Figure 4.5: A plot of training time's impact on ANN accuracy.

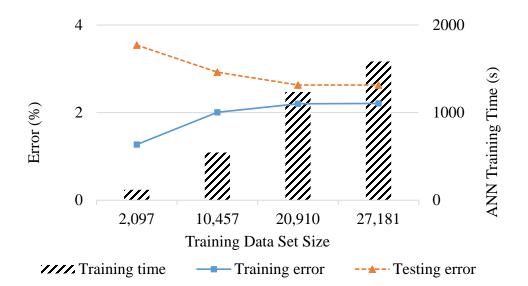

The third issue explored was how the size of training data influences the quality of the ANN. Figure 4.7, which plots the control-1 TP ANN error with respect to training data size, shows that small training data size created an inferior ANN, but large data sizes increased ANN training time with minimal returns on ANN quality. Different sizes of training data were collected and used to train the ANNs: 0.1%, 0.5%, 0.9%, and 1.5% of all TP locations in all training circuits. From this, the ANN with the lowest error was chosen: the total training samples/sub-circuits was 11,561, the data collecting time was 33.6 minutes, and the ANN training time was 16.3 minutes. This 50-minute overhead was considered with evaluating the computational efficiency of ANN TPI.

Figure 4.6: A plot on the number of neuron's on ANN accuracy.

Figure 4.7: A plot of training data size on ANN accuracy.

#### 4.8.2 TPI Experiment Results

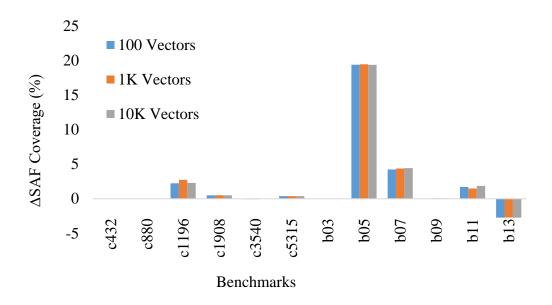

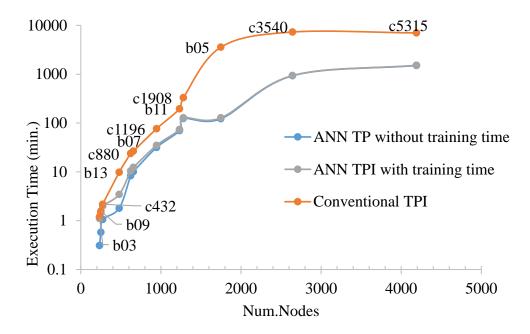

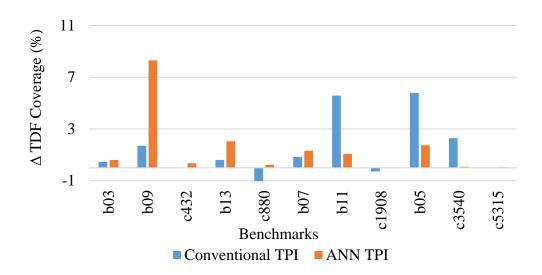

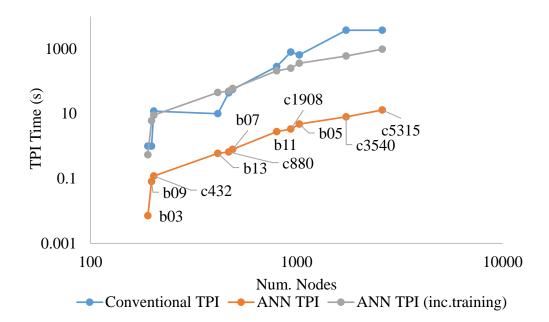

The results of fault simulation on benchmark circuits are shown in Table 4.2. First, this table shows the final fault coverage for three variations of benchmark circuits: with no TPs, after ANN TPI was performed, and after conventional TPI [33] was performed, with the conventional TPI using the same information used for ANN training (i.e., neither the ANN nor conventional TPI have an information advantage). These three circuit variations were fault simulated with 100, 1,000, and 10,000 vectors to confirm the effect of TPs was consistent under different stimulus conditions. For both TPI methods, the number of TPs inserted is listed under "num. TPs", which was limited to 1% of the total number of nets or predicted fault coverage limits or negative TP impact limits were never reached for any benchmark. Second, the table lists the time required to perform TPI for both ANN TPI and conventional TPI [33]. To account for random stimulus variation, the average fault coverage was recorded amongst multiple trials: 100 trials for 100 vectors, 50 trials for 1,000 vectors, and 10 trials for 10,000 vectors.

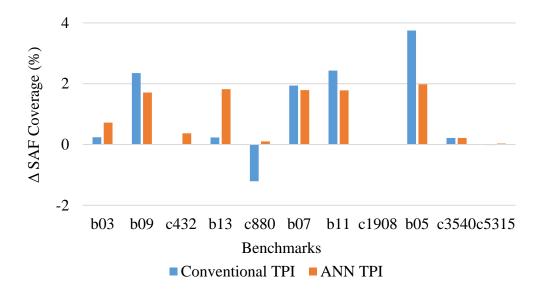

Table 4.2 shows the fault coverage created from TPs inserted by the ANN TPI algorithm was decisively superior compared to conventional TPI. This is better illustrated in Figure 4.8, which gives the relative fault coverage obtained by the ANN TPI compared to conventional TPI. These results revealed several findings. First, the fault coverage of ANN TPI was frequently higher, with the only benchmark providing lower fault coverage being b13. Second, it was noteworthy that extreme differences in fault coverage favor ANN TPI, as is demonstrated by the benchmark b05.

| Benchmarks            |                                       |      | c432      | c880  | c1196 | c1908  | c3540       | c5315       | b01          | b03       | b05         | b07       | b09       | b11        | b13       |

|-----------------------|---------------------------------------|------|-----------|-------|-------|--------|-------------|-------------|--------------|-----------|-------------|-----------|-----------|------------|-----------|

|                       | Num. TPs                              |      |           | 3     | 5     | 8      | 16          | 23          | 0            | 1         | 9           | 3         | 1         | 7          | 2         |

|                       | Num. nets                             |      | 196       | 443   | 561   | 913    | 1719        | 2485        | 47           | 156       | 962         | 433       | 169       | 764        | 352       |

|                       | Num. exp. nets                        |      |           | 682   | 978   | 1315   | 2693        | 4396        | 80           | 268       | 1783        | 706       | 280       | 1271       | 543       |

| Pro                   | ocessor memory                        | (MB) | 4         | 11    | 21.7  | 154.5  | 170         | 227.1       | $\backslash$ | 3.6       | 42.6        | 9.2       | 9.9       | 32.5       | 5.9       |

|                       | Num. Vect                             | ors  |           |       |       |        |             |             |              |           |             |           |           |            |           |

|                       |                                       | 100  | 92.3<br>7 | 90.31 | 66.99 | 75.86  | 80.50       | 94.30       | 100          | 98.<br>12 | 66.63       | 88.<br>71 | 79.<br>86 | 80.2<br>4  | 89.<br>94 |

|                       | No TPs                                | 1K   | 98.5<br>8 | 97.26 | 87.14 | 94.60  | 94.47       | 99.18       | 100          | 99.<br>98 | 75.50       | 92.<br>76 | 84.<br>60 | 92.0<br>6  | 94.<br>52 |

|                       |                                       | 10K  | 98.8<br>4 | 99.71 | 92.97 | 99.73  | 96.38       | 99.41       | 100          | 100       | 80.04       | 97.<br>55 | 98.<br>56 | 95.3<br>8  | 95.<br>78 |

| e (%)                 | ANN TPI                               | 100  | 98.8<br>2 | 99.86 | 94.23 | 99.69  | 96.40       | 99.44       |              | 99.<br>99 | 83.00       | 97.<br>52 | 99.<br>57 | 95.9<br>1  | 95.<br>75 |

| SAF coverage (%)      |                                       | 1K   | 98.8<br>3 | 99.84 | 94.65 | 99.83  | 96.38       | 99.44       |              | 100       | 82.95       | 97.<br>68 | 99.<br>02 | 95.6<br>6  | 95.<br>75 |

| SAF c                 |                                       | 10K  | 98.8<br>4 | 100   | 94.35 | 99.91  | 96.47       | 99.44       |              | 100       | 83.03       | 97.<br>75 | 99.<br>91 | 96.0<br>7  | 95.<br>79 |

|                       | Conventiona<br>1 TPI                  | 100  | 98.8<br>2 | 99.85 | 92.00 | 99.19  | 96.45       | 99.06       |              | 99.<br>99 | 63.62       | 93.<br>28 | 99.<br>53 | 94.2<br>0  | 98.<br>48 |

|                       |                                       | 1K   | 98.8<br>3 | 99.82 | 91.92 | 99.32  | 96.43       | 99.06       |              | 100       | 63.50       | 93.<br>30 | 98.<br>96 | 94.1<br>8  | 98.<br>47 |

|                       |                                       | 10K  | 98.8<br>4 | 100   | 92.06 | 99.41  | 96.47       | 99.06       |              | 100       | 63.66       | 93.<br>32 | 99.<br>85 | 94.2<br>1  | 98.<br>52 |

|                       |                                       | 100  | 1.14      | 7.32  | 30.94 | 128.72 | 967.5<br>1  | 1568.<br>82 | $\bigcirc$   | 0.3<br>8  | 131.6<br>2  | 10.<br>79 | 0.5<br>8  | 72.9<br>0  | 2.0<br>0  |

|                       | ANN TPI                               | 1K   | 1.09      | 7.17  | 30.43 | 124.62 | 894.4<br>3  | 1488.<br>73 | $\searrow$   | 0.1<br>1  | 122.5<br>1  | 9.9<br>7  | 0.5<br>5  | 68.5<br>9  | 1.8<br>0  |

| <u>.</u>              |                                       | 10K  | 1.06      | 8.31  | 31.65 | 123.63 | 930.0<br>1  | 1508.<br>25 | $\searrow$   | 0.3<br>1  | 122.1<br>9  | 10.<br>08 | 0.5<br>8  | 69.6<br>7  | 1.8<br>0  |

| e (min                |                                       | 100  | 2.08      | 9.46  | 34.19 | 133.12 | 976.5<br>9  | 1583.<br>21 | $\searrow$   | 1.1<br>8  | 137.6<br>2  | 13.<br>04 | 1.4<br>4  | 77.1<br>3  | 3.6<br>5  |

| Execution time (min.) | ANN TPI<br>including<br>training time | 1K   | 2.03      | 9.31  | 33.68 | 129.02 | 903.5<br>1  | 1503.<br>12 | $\searrow$   | 0.9<br>1  | 128.5<br>1  | 12.<br>22 | 1.4<br>1  | 72.8<br>2  | 3.4<br>5  |

| xecuti                |                                       | 10K  | 2.00      | 10.45 | 34.90 | 128.03 | 939.0<br>9  | 1522.<br>64 |              | 1.1<br>1  | 128.1<br>9  | 12.<br>33 | 1.4<br>4  | 73.9<br>0  | 3.4<br>5  |

| Е                     |                                       | 100  | 2.27      | 23.14 | 75.50 | 323.87 | 7321.<br>71 | 7199.<br>80 |              | 1.2<br>5  | 4004.<br>53 | 27.<br>12 | 1.6<br>2  | 204.<br>02 | 10.<br>06 |

|                       | Conventiona<br>1 TPI                  | 1K   | 2.36      | 23.31 | 78.39 | 323.37 | 5302.<br>20 | 7015.<br>34 |              | 1.3<br>1  | 482.7<br>2  | 25.<br>90 | 1.5<br>6  | 195.<br>05 | 10.<br>02 |

|                       |                                       | 10K  | 2.17      | 23.77 | 76.44 | 329.86 | 7314.<br>74 | 7003.<br>95 |              | 1.2<br>0  | 3578.<br>09 | 26.<br>53 | 1.5<br>6  | 195.<br>57 | 9.8<br>0  |

# Table 4.2: ANN TPI and Conventional TPI Targeting SAF Experimental Results

Figure 4.8: ANN and conventional TPI targeting SAF in SAF coverage comparison.